# Design and FPGA Implementation of Dual Self-Tuning Filter based Controller for Single Phase Shunt Active Filter

Pavana Gurudas Bhat

B.Tech Student

Dept. of E & E

NITK Surathkal

Mangalore, India

pavanagbhat97@gmail.com

Disha R Shetty

B.Tech Student

Dept. of E & E

NITK Surathkal

Mangalore, India

dishashetty1997@gmail.com

Jayasankar V N

Research Scholar

Dept. of E & E

NITK Surathkal

Mangalore, India

jayasankarvn@gmail.com

Vinatha U

Senior IEEE Member

Associate Professor

Dept. of E & E

NITK Surathkal

Mangalore, India

u vinatha@yahoo.co.in

Abstract—The use of power electronic devices injects harmonics into the grid causing serious power quality problems. To limit the current harmonics in accordance with IEEE Std 519, Shunt Active Power Filter (SAPF) may be used. Instantaneous power theory (pq theory) is widely used for current harmonic mitigation in SAPF. The Low Pass Filter (LPF) is used in pq theory based controllers for fundamental component extraction. The drawbacks of LPF are additional phase delay at the fundamental frequency and presence of lower frequency oscillations. A dual Self-Tuning Filter based controller is proposed to overcome these limitations. The simulation studies under different system conditions are carried out using MATLAB/SIMULINK to verify the effectiveness of the proposed method. The hardware cosimulation using ZedBoard Zynq-7000 Development Board is carried out to validate the simulation results.

Index Terms—Shunt Active Power Filter, pq-theory, PI controller, Self Tuning Filter, Current harmonic mitigation

# I. INTRODUCTION

The use of power electronic devices are increasing exponentially. These devices inject harmonics into the grid, which leads to a serious distortion of the power supply current and voltage, decreasing the quality of power supply. Passive and active filters can be used for harmonic compensation. However, passive LC filters are bulky, load dependent and inflexible. They can also cause resonance problems in the system. To overcome these disadvantages, shunt active power filters (SAPF) are introduced, which compensate for the current harmonics and reduce the total harmonic distortion (THD).

Shunt Active Filter based controller has two control loops i.e DC-link Voltage Control and Current harmonic mitigation. There are two classes of methods for current harmonics mitigation: the frequency methods and the time domain methods. The frequency methods are based on the Fast Fourier Transformation (FFT) [1] and the Recursive Discrete Fourier Transformation (RDFT) [2]. These methods involve heavy calculation and require a lot of memory. The time domain methods are more preferred because of their fast response and simple design. Some of the commonly used time domain methods are the p-q method of instantaneous power [3]–[6]

and the d-q method (fundamental frequency and/or higher harmonics) [7]. Implementation of pq method [8] is simple. However, it has a limitation of poor performance under distorted grid conditions. From literature, it is observed that the pq method uses a low pass filter (LPF) [9] for fundamental component extraction. The limitations of LPF are phase delay at fundamental frequency and presence of lower frequency oscillations.

In this paper, a dual self-tuning filter (STF) based pq method is used for current harmonic mitigation to overcome the drawbacks of the classical pq method. PI controller is used for DC link voltage control.

# II. SYSTEM DESCRIPTION

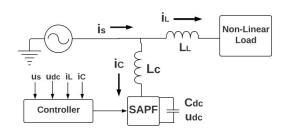

The block diagram of a single phase SAPF is in Fig 1, where  $i_s$  is the source current,  $i_l$  is the load current,  $i_c$  is the current used for compensating the load harmonics and reactive power,  $u_s$  is the source voltage. The SAPF comprises of a DC link capacitor ( $C_{dc}$ ), a filter inductor ( $L_c$ ) and a single-phase voltage source inverter with four controllable switches.  $u_{dc}$  is the voltage across  $C_{dc}$  and  $L_l$  is the surge impedance.

Fig. 1: Block diagram of single-phase SAPF

## III. CONTROLLER DESIGN

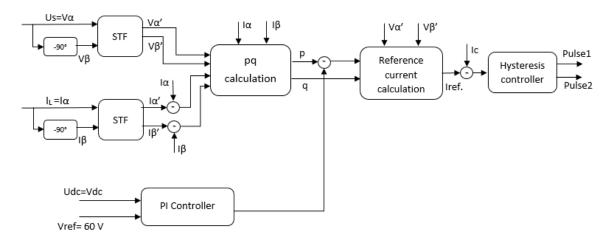

The block diagram of a SAPF control scheme is shown in Fig.2. It consists of a PI controller, Reference current calculator and Hysteresis controller. Source voltage and load

Fig. 2: Block diagram of single-phase SAPF controller

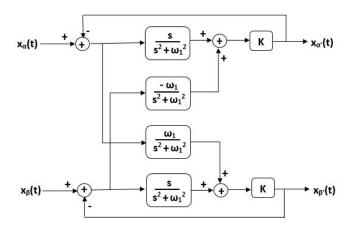

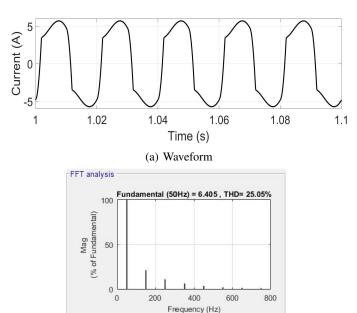

current are sensed and transformed into a fictitious alpha-beta frame by adding a delay of 90°. These signals are then fed as inputs to two STFs. STF extracts the fundamental component of the signal with zero phase delay. The harmonic component of the load current is obtained by subtracting the output of the STF from the original signal. p and q are then calculated by using equations (2) and (3). PI controller is used for DC link voltage control. The output of the PI controller is subtracted from the p component. The reference current is calculated using equations (4) and (5). The reference current is then subtracted from the compensation current and the error is then fed as inputs to the hysteresis current controller so as to generate the desired pulses.

## A. Self-tuning Filter

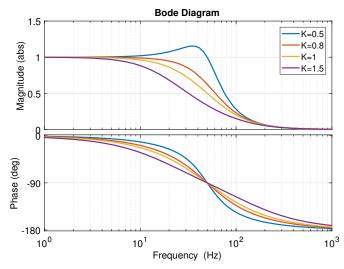

Fig 3 shows the frequency response of LPF for fundamental frequency of 50Hz. It can be observed that, there is a phase delay and attenuation at the fundamental frequency.

Fig. 3: Bode Plots of second order LPF

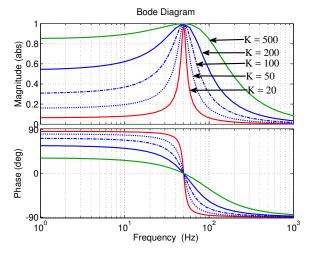

STF [10] has zero attenuation and zero phase delay at the fundamental frequency. The frequency response of STF is shown in Fig 4. It acts as an integrator in the alpha-beta

Fig. 4: Bode Plot of STF

domain. The block diagram of STF is attached in Fig.5. The resonant frequency for integrator is  $\omega$ . The integrator output is negligible for frequencies other than  $\omega$ . The gain K and the feedback loop act as an error correction part of the circuit. Hence, by choosing the desired frequency  $\omega_1$ , the required output can be obtained. The transfer function of STF is given as:

$$H(s) = K \frac{s + K + j\omega_1}{(s + K)^2 + (\omega_1)^2}$$

(1)

## B. p-q Calculation

The p-q theory is a generalized theory of the instantaneous reactive power in three-phase circuits. It is a tool used for the control of active power and analysis of three phase power systems in order to detect problems related to harmonics, reactive power and unbalance [3]. The equations of p-q

Fig. 5: Block diagram of Self-tuning filter

calculations are as follows:

$$p = V_{\alpha'}(I_{\alpha h}) + V_{\beta'}(I_{\beta h}) \tag{2}$$

$$q = V_{\alpha'} I_{\beta} - V_{\beta'} I_{\alpha} \tag{3}$$

Here, p is the instantaneous active power and q is the instantaneous reactive power.  $V_{\alpha'}$  and  $V_{\beta'}$  are the fundamental components of the source voltage.  $I_{\alpha h}$  and  $I_{\beta h}$  are the harmonic components of the load current.  $I_{\alpha'}$  and  $I_{\beta'}$  are the fundamental components of load current.

#### C. PI Controller

PI controller consists of a feedback control loop that calculates an error signal by taking the difference between the output of the system and the reference point. The transfer function of PI controller is of the form  $(K_p + \frac{K_i}{s})$  where  $K_p$  and  $K_i$  are constants.

## D. Reference Current Calculation

The equations to calculate the reference compensation currents are given by:

$$I_{\alpha\_ref} = \frac{V_{\alpha'} * p - V_{\beta'} * q}{V_{\alpha'}^2 + V_{\beta'}^2}$$

(4)

$$I_{\beta\_ref} = \frac{V_{\beta'} * p + V_{\alpha'} * q}{V_{\alpha'}^2 + V_{\beta'}^2}$$

(5)

Here,  $I_{\alpha\_ref}$  is the reference alpha current and  $I_{\beta\_ref}$  is the reference beta current.

# E. Hysteresis Controller

Hysteresis controller compares the Voltage Source Inverter (VSI) current with that of the reference current and pulses are generated accordingly. These pulses are given as gating signals to the switches of VSI. The logic of hysteresis current control is as follows:

If  $i_c$  is less than  $(i_{ref}$  - HB)  $S_1$ ,  $S_4$  ON and  $S_2$ ,  $S_3$  OFF If  $i_c$  is greater than  $(i_{ref}$  + HB)  $S_1$ ,  $S_4$  OFF and  $S_2$ ,  $S_3$  ON

Here,  $S_1$ ,  $S_3$  are the upper switches of the two legs and  $S_2$ ,  $S_4$  are the lower switches. HB is the hysteresis band.  $i_c$  is the compensation current and  $i_{ref}$  is the reference current calculated.

# IV. RESULTS

The system is designed using MATLAB/Simulink and Xilinx System Generator. A Programmable voltage source is used to simulate grid voltage and rectifier connected RL load forms the non-linear load. The reference voltage for PI controller is taken as 60V. The specifications of the various components used are shown in Table I

TABLE I: Specifications of Components

| Components | Description                                             |

|------------|---------------------------------------------------------|

| Source     | Single phase AC source, 30Vrms, 50Hz                    |

| RL load    | 5Ω, 30mH                                                |

| Capacitor  | 2 capacitors of 4.7nF                                   |

| FPGA       | ZedBoard [Xilinx Zynq-7000 all programmable SoC(APSoC)] |

#### A. Simulation Results

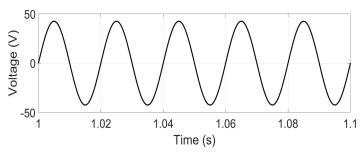

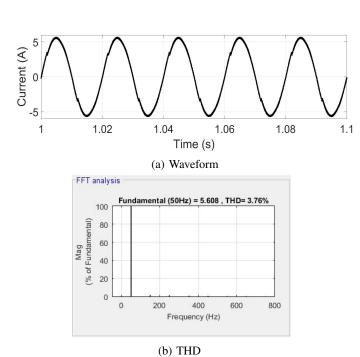

1) Steady State Analysis with ideal source: In this case, the system is tested under non-distorted voltage source and constant load. The waveform and the THD of the source voltage is shown in Fig 6a and Fig 6b respectively.

(a) Waveform

(b) THD

Fig. 6: Ideal source voltage u<sub>s</sub>

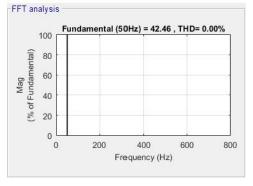

The load current is non-linear as shown in Fig 7a. The THD of the load current is 25.05% as shown in Fig 7b. If compensation is not done, the source current is same as distorted load current. Due to SAPF, harmonics are reduced

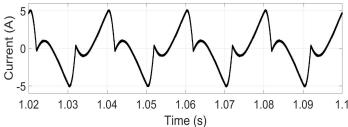

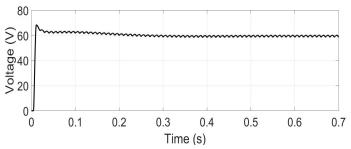

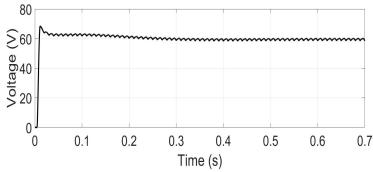

to a THD of 3.76% which comply with the IEEE-519 [11]. Source current is shown in Fig 8a and THD is shown in Fig 8b. Compensation current is the current injected by the SAPF in the grid as shown in Fig 9. The voltage across the capacitor is shown in Fig 10. It can be observed that  $\mathbf{u}_{dc}$  settles down to 60V.

(b) THD Fig. 7: Load current  $i_l$  for ideal source voltage

Fig. 8: Source current i<sub>s</sub> for ideal source voltage

Fig. 9: Compensation current  $i_c$  for ideal source voltage

Fig. 10: Voltage across capacitor  $(u_{dc})$  for ideal source voltage

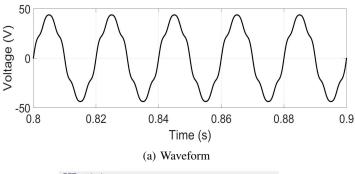

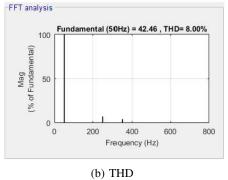

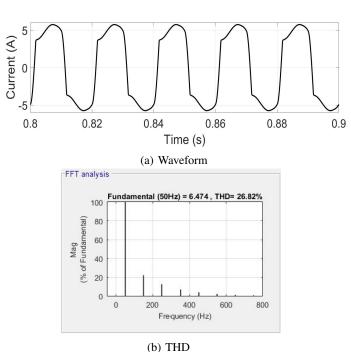

2) Steady State Analysis with distorted source: The distorted voltage source of 8% THD (7% of the fifth harmonic and 3.87% of the seventh harmonic) is used and is shown in Fig 11a. The THD of the source voltage is shown in Fig 11b.

Fig. 11: Source voltage u<sub>s</sub> with 8% harmonics

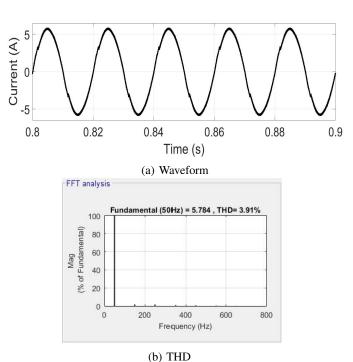

The waveform and the THD of load current and source current are shown in Fig 12a, Fig 12b, Fig 13a and Fig

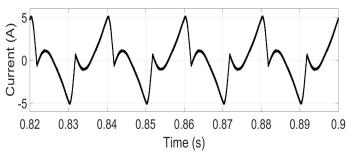

13b respectively. The THD of the load current is 26.82% and source current has THD of 3.91%. The waveform of compensation current is shown in Fig 14. The voltage across the capacitor settles down to 60V as shown in Fig 15.

Fig. 12: Load current i<sub>l</sub> for 8% harmonics in source

Fig. 13: Source current i<sub>s</sub> for 8% harmonics in source

Fig. 14: Compensation current i<sub>c</sub> for 8% harmonics in source

Fig. 15: Voltage across capacitor ( $u_{dc}$ ) for 8% harmonics in source

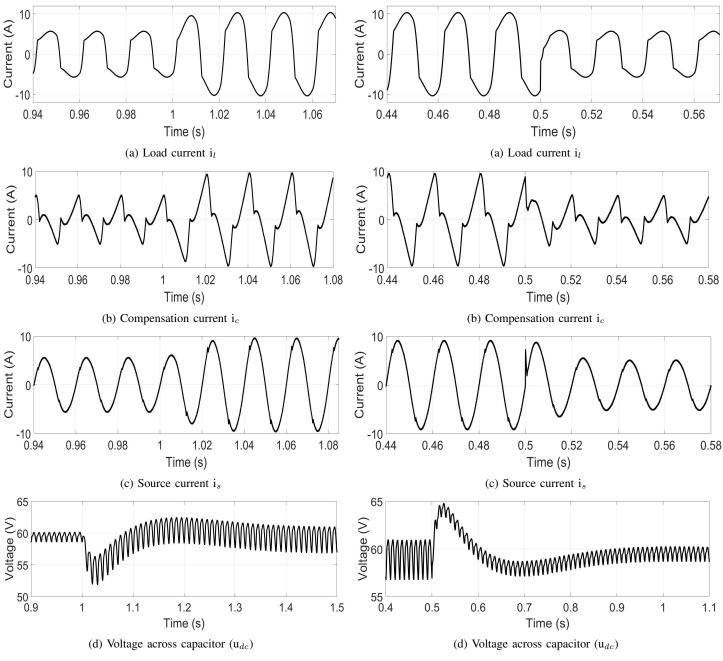

3) Dynamic analysis with ideal source: At 1s, when the load is decreased by 50%, the load current, the compensation current and the source current are shown in Fig 16a, Fig 16b and Fig 16c respectively. It can be observed that as the load is decreased, the load current, the compensation current and the source current are increased by 100%. The voltage across capacitor changes at 1s due to the system dynamics, but it settles down to 60V after 2-3 cycles as shown in Fig 16d.

At 0.5s, when the load is increased by 100%, the load current, the compensation current and the source current are shown in Fig 17a, 17b and Fig 17c respectively. As the load is increased, the load current, the compensation current and the source current are decreased by 50%. The voltage across capacitor changes at 0.5s due to the system dynamics, but it settles down to 60V after 2-3 cycles as shown in Fig 17d.

Fig. 16: Results for decrease in load

Fig. 17: Results for increase in load

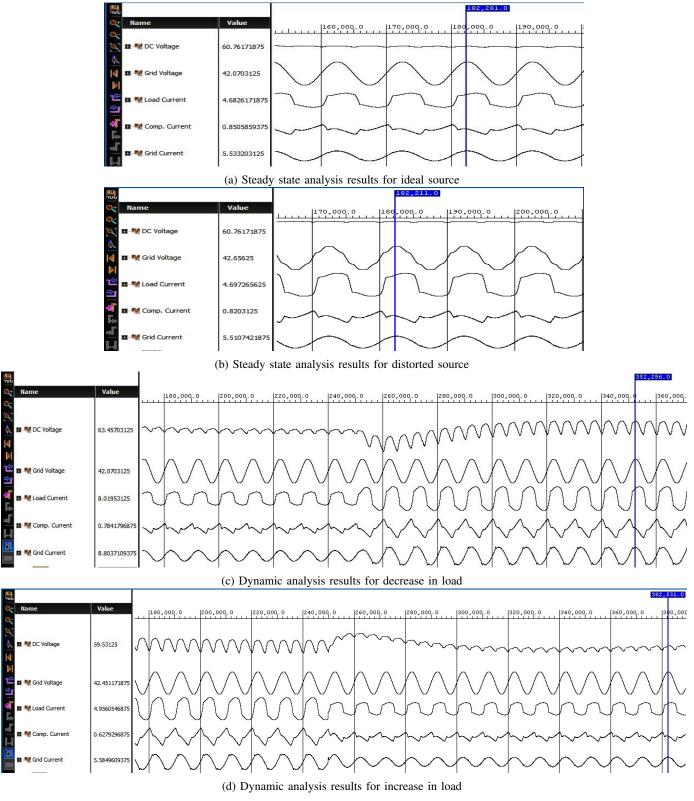

#### B. Hardware Co-simulation Results

In hardware co-simulation, the controller is implemented using FPGA and power circuit is implemented in MATLAB and the results are analyzed. Hardware co-simulation was performed using Zedboard FPGA with the help of the Xilinx System Generator. The waveforms obtained for steady state ideal grid voltage conditions are shown in Fig 18a. DC link voltage, grid voltage, load current, compensation current and grid current can be seen in the figure. Fig 18b shows DC link voltage, grid voltage, load current, compensation current and grid current under distorted grid conditions (8%

harmonics). The waveforms obtained for ideal grid voltage and dynamic decrease (50%) in the load are shown in Fig 18c. The figure shows DC link voltage, grid voltage, load current, compensation current and grid current. The waveforms obtained for ideal grid voltage and dynamic increase (50%) in load are shown in Fig 18d. In the figure, DC link voltage, grid voltage, load current, compensation current and grid current can be observed.

For all the above cases, it can be observed that the results obtained from hardware co-simulation are same as that of MATLAB simulation results.

Fig. 18: Hardware Co-simulation results

#### V. CONCLUSION

The use of dual STF based SAPF helps to mitigate harmonics in single phase circuits with non-linear loads. Reactive power required by the nonlinear load is completely compensated by SAPF and power factor at source end becomes almost unity. THD of source current is reduced to less than 5% by using SAPF. DC link voltage is maintained constant irrespective of load changes and source distortions. So, it can be concluded that dual STF based controller for SAPF is efficient and it overcomes the drawbacks of classical pq method.

#### REFERENCES

- S. S. Wategaonkar, S. S. Patil and P. R. Jadhav, "Mitigation of Current Harmonics Using Shunt Active Power Filter," 2018 3rd International Conference for Convergence in Technology (I2CT), Pune, 2018, pp. 1-5

- [2] M. Karbasforooshan and M. Monfared, "An adaptive recursive discrete fourier transform technique for the reference current generation of single-phase shunt active power filters," 2016 7th Power Electronics and Drive Systems Technologies Conference (PEDSTC), Tehran, 2016, pp. 253-259.

- [3] J. L. Afonso, M. J. S. Freitas and J. S. Martins, "p-q Theory power components calculations," 2003 IEEE International Symposium on Industrial Electronics (Cat. No.03TH8692), Rio de Janeiro, Brazil, 2003, pp. 385-390 vol. 1.

- [4] M. Karbasforooshan and M. Monfared, "Design and implementation of a single-phase shunt active power filter based on PQ theory for current harmonic compensation in electric distribution networks," IECON 2017

- 43rd Annual Conference of the IEEE Industrial Electronics Society, Beijing, 2017, pp. 6389-6394.

- [5] H. Akagi, Y. Kanazawa, A. Nabae, "Generalized Theory of the Instantaneous Reactive Power in Three-Phase Circuits", IPEC'83 Int. Power Electronics Conf., pp. 1375-1386, 1983.

- [6] A. H. Ukande, S. L. Tiwari, S. G. Kadwane and A. Kadu, "Generalise PQ theory with SPWM for single phase shunt active filter applications," 2015 IEEE Power, Communication and Information Technology Conference (PCITC), Bhubaneswar, 2015, pp. 89-94.

- [7] C. V. Suru, C. A. Patrascu and M. Linca, "The synchronous fundamental dq frame theory implementation and adaptation for the active filtering," 2014 International Conference on Applied and Theoretical Electricity (ICATE), Craiova, 2014, pp. 1-6.

- [8] M. Aredes and L. F. C. Monteiro, "A control strategy for shunt active filter," 10th International Conference on Harmonics and Quality of Power. Proceedings (Cat. No.02EX630), Rio de Janeiro, 2002, pp. 472-477 vol.2.

- [9] R. Chudamani, K. Vasudevan and C. S. Ramalingam, "Comparative Evaluation of Harmonic Extraction Techniques for Three-Phase Three-Wire Active Power Filter," 2007 7th International Conference on Power Electronics and Drive Systems, Bangkok, 2007, pp. 1700-1706.

- [10] S. Aravind, U. Vinatha and V. N. Jayasankar, "Wind-solar grid connected renewable energy system with series active self tuning filter," 2016 International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT), Chennai, 2016, pp. 1944-1948.

- [11] IEEE Recommended Practice and Requirements for Harmonic Control in Electric Power Systems," in IEEE Std 519-2014 (Revision of IEEE Std 519-1992), vol., no., pp.1-29, 11 June 2014