# Low power fully differential, feed-forward compensated bulk driven OTA

Rekha S. and Laxminidhi T.

Department of Electronics and Communication Engineering

National Institute of Technology Karnataka,

Surathkal – 575025 INDIA

rsbhat 99@yahoo.com, laxminidhi t@yahoo.com

Abstract— A low voltage, low power bulk driven Operational Transconductance Amplifier (OTA) is designed in 180 nm CMOS Technology. The OTA employs feed-forward compensation achieving open loop DC gain of 44.05 dB, 3 dB bandwidth of 408 kHz, Unity Gain Bandwidth (UGB) of 9.07 MHz. OTA is stable with phase margin of 45° and a gain margin of 66 dB for a pure capacitive load of 1 pF. OTA operates on 0.5 V supply consuming a power of 30 μW.

Keywords- CMOS; bulk driven; feed-forward frequency compensation

#### I. INTRODUCTION

Continuous time filters demanding high dynamic range for a given power are often realized using active-RC integrators. Operational amplifier (OPAMP) is the main building block of the active-RC integrator. However, the low output impedance requirement of OPAMP makes it power hungry. For this reason, Operational Transconductance Amplifiers (OTAs) are widely used in place of OPAMPs but with some careful design [1,2]. Design of OTA becomes more challenging as the technology scales down, due to the fact that the supply voltage scales down while the threshold remains relatively constant. A bulk driven OTA was proposed by A. Guzinski [3] in 1987 to overcome threshold voltage issue. The research there on led to many bulk-driven OTA designs, for example [4]. This paper presents the design of a low power OTA for low power applications.

The common Miller compensation scheme used to stabilize the OTA in feedback, suffers from poor gain-bandwidth product. When such a OTA is used to realize a filter, the realizable filter bandwidth is limited by the OTA gain-bandwidth. Feed-forward compensation scheme is found to be effective in pushing the gain-bandwidth product of the OTA to a higher value [5,6,7].

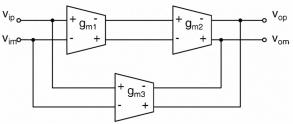

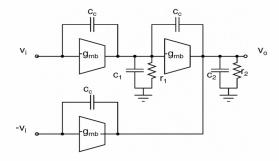

## II. FEED-FORWARD OTA

The block schematic of fully differential feed-forward compensated OTA is shown in Fig. 1 [7]. In the figure,  $g_{m1}$  and  $g_{m2}$  are fully differential transconductors forming the forward path of the OTA and  $g_{m3}$ , also a fully differential transconductor, forming the feed-forward path. A simplified single ended model of the OTA in Fig. 1 is shown in Fig. 2. The corresponding transfer function can be written as follows.

Fig.1 Fully differential feed-forward compensated OTA

Fig.2 Single ended Feed-forward compensated OTA

$$\frac{V_o}{V_i} = \frac{g_{m1}g_{m2}r_1r_2\left[1 + \frac{s}{\omega_z}\right]}{\left[1 + \frac{s}{\omega_{p1}}\right]\left[1 + \frac{s}{\omega_{p2}}\right]} \tag{1}$$

where

$$\omega_{p1} = \frac{1}{r_1 c_1}$$

,  $\omega_{p2} = \frac{1}{r_2 c_2}$  and  $\omega_z = \frac{\omega_{p1} g_{m1} g_{m2} r_1}{g_{m3}}$ .

The feed-forward path thus introduces a left half s-plane zero at  $s = -\omega_z$  which improves the phase margin of the OTA without compromising the band width.

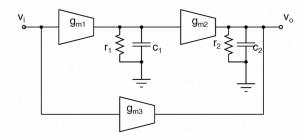

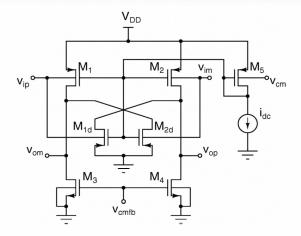

# III. FULLY DIFFERENTIAL BULK DRIVEN TRANSCONDUCTOR

It is a common practice to use source coupled differential pair to realize the transconductor. But due to the limitations on overhead when operating with low supply voltages, it is common to use a pseudo differential architecture. A pseudo differential transconductor is shown in Fig. 3. In the figure,  $v_{\rm ip}$  and  $v_{\rm im}$  are the differential inputs and  $v_{\rm op}$  and  $v_{\rm om}$  are the differential outputs.  $M_1$  and  $M_2$  are the input transistors

operating in saturation.  $M_3$  and  $M_4$  form the NMOS loads and operate in weak inversion.

Fig. 3 Pseudo differential bulk driven transconductor

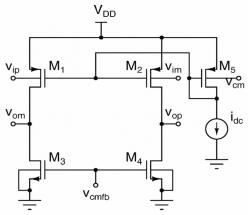

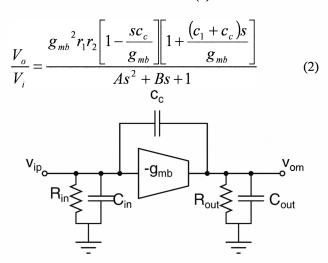

A single ended small signal equivalent circuit of the differential transconductor is shown in Fig. 4. In the figure,  $g_{mb}$  is the transconductance of bulk driven transistor ( $M_1/M_2$ ).  $C_{in}$  and  $C_{out}$  are the effective capacitances at input and output respectively. Similarly,  $R_{in}$  and  $R_{out}$  are the effective input and output resistances respectively.  $C_c$  is the effective coupling capacitance between the input and the output (bulk and the drain). This coupling capacitance can not be ignored as it is the drain junction capacitance and it introduces a right half plane zero. A simple scheme to compensate for this effect is shown in Fig. 5. It is to be noted that this will only compensate for the capacitance but will not cancel the capacitance altogether.

#### IV. BULK DRIVEN FEED-FORWARD OTA

Bulk driven feed-forward OTA shown in Fig. 1 is realized using the differential transconductor shown in Fig. 5. Single ended small signal equivalent circuit of the differential feed-forward OTA is shown in Fig. 6 and the corresponding transfer function can be written as in (2).

Fig.4 Single ended small signal model of the transconductor

Fig. 5 Fully differential Bulk driven Transconductor

where

$$A = r_1 r_2 \left( c_1 c_2 + 2 c_c c_1 + 2 c_c c_2 + 3 c_c^2 \right),$$

$$B = r_1 c_1 + r_2 c_2 + g_{mb} r_1 r_2 c_2$$

and  $r_1$ ,  $c_1$  and  $r_2$ ,  $c_2$  represent the effective impedance seen at the intermediate node of the forward path and output respectively with respect to small signal ground. In (2), it can be seen that there are two zeros, one on the left half of s-plane

(at

$$\frac{-g_{mb}}{c_1 + c_c}$$

) and the other on the right half of s-plane (at

$\frac{g_{mb}}{c_c}$ ). While the left half plane zero is introduced by the

feed-forward transconductor to compensate the OTA, the right half plane zero is introduced due to the coupling capacitance,  $c_c$ . Note that the transistors  $M_{1d}$  and  $M_{2d}$  in Fig. 5 attempt to reduce  $c_c$  to a minimum so that the effect of right half plane zero is minimized.

Fig.6 Small signal model of feed-forward OTA

#### V. SIMULATION RESULTS

A bulk driven differential transconductor is designed in 180 nm technology to operate at 0.5 V supply. The input and output common mode voltages of the transconductor are fixed at 0.25 V. In Fig. 5, gates of  $M_1$  and  $M_2$  are biased to carry a quiescent current of 10  $\mu A$  and are sized for a bulk transconductance of 45  $\mu S$ . Gates of  $M_3$  and  $M_4$  are biased

with a common mode feedback voltage which sets the output common mode voltage. Transconductor is modeled and modeled values are as follows.

$\begin{array}{lll} R_{in} &=& 14.36 \ M\Omega \\ R_{out} &=& 385.8 \ k\Omega \\ C_{in} &=& 443.577 \ fF \\ C_{out} &=& 189.632 \ fF \end{array}$

$C_c = 0.68248$  fF after compensation.

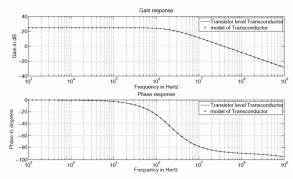

It is worth noting that, without the compensation, C<sub>c</sub> was 47 fF. Fig. 7 compares the frequency response of the transistor level transconductor and that of its model.

Fig.7 Frequency response of Transistor level differential Transconductor and of its model

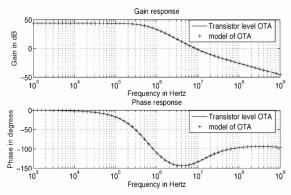

A bulk driven feed-forward compensated OTA then built using the transconductors. Fig. 8 compares the frequency response of the transistor level differential OTA and of its model (Fig. 4). OTA has an open loop DC gain of 44 dB. Under no load condition the OTA has a 3 dB bandwidth of 601 kHz, UGB of 22 MHz, phase margin of 68.5° and a gain margin of 54.89 dB. It is to be noted that, if it were a Miller compensation, for the same UGB of 22 MHz, the 3-dB bandwidth would have been 138 kHz. For a pure capacitive load of 1 pF, OTA has 3 dB bandwidth of 408 kHz, UGB of 9.07 MHz, a phase margin of 45° and a gain margin of 66 dB. If resistive loads are considered, the phase margin is sure to be improved as the damping increases. Table I lists the parameters of the OTA. A comparison of performance parameters of the designed OTA with other low voltage OTAs found in the literature is listed in Table II.

Fig. 8 Frequency response of feed-forward OTA

TABLE 1 PARAMETERS OF OTA

| Paran                 | Simulat<br>ed<br>values<br>of OTA |       |

|-----------------------|-----------------------------------|-------|

| Supply [V]            | 0.5                               |       |

| Open loop DC gain [dB | 44                                |       |

|                       | No load                           | 601   |

| 3 dB bandwidth [kHz]  | I pF capacitive load              | 408   |

|                       | No load                           | 22    |

| UGB [MHz]             | I pF capacitive load              | 9.07  |

|                       | No load                           | 68.5  |

| Phase margin [degree] | I pF capacitive load              | 45    |

|                       | No load                           | 54.89 |

| Gain margin [dB]      | I pF capacitive load              | 66    |

| Power [μW]            | 30 *                              |       |

| Technology [µm]       | 0.18                              |       |

| Input referred        | @10 kHz                           | 95.8  |

| noise [nV/√Hz]        | @1 MHz                            | 65.72 |

<sup>\*</sup> excluding CMFB circuit

TABLE II COMPARISON WITH OTHER LOW VOLTAGE OTA DESIGNS

| Parameter                                          | [4]  | [8]  | [9]  | [10] | [11]  | [12] | Present<br>work |

|----------------------------------------------------|------|------|------|------|-------|------|-----------------|

| Supply (V)                                         | 0.5  | 1    | 1    | 0.8  | 0.9   | 1.3  | 0.5             |

| DC gain<br>(dB)                                    | 52   | 70   | 49   | 53   | 70    | 84   | 44              |

| UGB<br>(MHz)                                       | 2.5  | 0.2  | 1.3  | 1.3  | 0.006 | 1.3  | 9.07            |

| Power (µW)                                         | 110  | 5    | 300  |      | 0.5   | 460  | 30 *            |

| Technology (μm)                                    | 0.18 | 0.35 | 2    | 0.5  | 2.5   | 0.7  | 0.18            |

| C <sub>L</sub> (pF)                                | 20   | 7    | 22   | 20   | 12    |      | 1               |

| Input<br>referred<br>noise @ 10<br>kHz<br>[nV/√Hz] | 220  | 260  | 181  |      |       |      | 95.8            |

| Input<br>referred<br>noise @ 1<br>MHz<br>[nV/√Hz]  | 90   |      | 43.6 |      |       |      | 65.72           |

<sup>\*</sup> excluding CMFB circuit

#### VI. CONCLUSIONS

A fully differential low power OTA is described. The OTA designed is in 180 nm CMOS technology and is feed-forward compensated. It has 44 dB DC gain, 9.07 MHz UGB, 45° phase margin and 66 dB gain margin at 1 pF pure capacitive load consuming a power of  $30\mu W$  from 0.5 V supply.

### REFERENCES

- [1] Wheatley C.F. and Wittlinge H. A., "OTA obsoletes OPAMP", Proceedings of National Econ. Conference I, pp.152-157, 1969.

- [2] Yannis P.Tsividis, "Integrated Continuous time filters design An Overview", IEEE Journal of solid state circuits, Vol. 29, No.3, pp. 166-176, March 1994.

- [3] A. Guzinski, M. Bialko and J. C. Matheau, "Body driven differential amplifier for applications in continuous time active-C filter", Proc. European Conf. Circuit Theory and Design (ECCTD'87), pp. 315-320, 1987.

- [4] Shouri Chatterjee, Yannis Tsividis, Peter Kinget, "0.5V Analog Circuit Techniques and their Application in OTA and filter design", IEEE Journal of Solid-state Circuits, Vol.40, No.12, pp. 2373-2387, December 2005.

- [5] J.N.Harrison and N.Weste, " 350 MHz Opamp-RC filter in 0.18  $\mu m$  CMOS", IEE Electronics Letters, pp.259-260, March 2002.

- [6] Tonse Laxminidhi, Venkata Prasadu and Shanthi Pavan, "Widely programmable high frequency active RC filters in CMOS technology", IEEE transactions on circuits & Systems, Vol.56, No.2, pp.327-336, February 2009.

- [7] B.Thandri and J.Silva Martinez, "A Robust feedforward compensation scheme for multistage operational Transconductance Amplifiers with no miller capacitors", IEEE J. Solid State Circuits, Vol.38, No.2, pp. 237-243, Feb. 2003

- [8] Kimmo Lasanen, Elvi Raisanen-Ruotsalainen, Juha Kostamovaara, "A 1- V 5μW CMOS-Opamp with Bulk-Driven Input Transistors", Proc. 43rd IEEE Midwest Symp. on Circuits and Systems, pp.1038-1041, Aug. 8-11, 2000

- [9] B. Blalock, P. Allen, and G.Rincon-Mora, "Designing 1-V op-amps using standard digital CMOS technology", IEEE Trans. Circuits Systems II, Analog Digital Signal Process Vol.45, no.7, pp. 769-780, July 1998.

- [10] T. Lehmann and M. Cassia, "1-V power supply CMOS cascode amplifier", IEEE J. Solid State Circuits, Vol.36, no.7, pp. 1082-1086, July 2001.

- [11] T. Stockstad and H. Yoshizawa, "A 0.9V- 0.5μA rail-to-rail CMOS operational amplifier", IEEE J. Solid State Circuits, Vol.37, pp. 286-292, 2002.

- [12] G. Ferri and W. Sansen, "A 1.3V opamp in standard 0.7 μm CMOS with constant g<sub>m</sub> and rail-to-rail input and output stages", IEEE Int. Solid State Circuits Conf. Dig. Tech. Papers, Vol. 478, 1996, pp. 382-383.